Area Suffix

# JVC SERVICE MANUAL

# AUDIO/VIDEO CONTROL RECEIVER

# RX-6010VBK RX-6018VBK

.I ----- U.S.A. JVC ጎጦሾ CIIC ിറിറ്റ JVC ्री **COMPULINK** 0 Õ 0 COMPUTING POWER ó Ö **1**||| **Remote** || **||** ) I G I T A L INPUT ANALOG INPUT DIGITAL ADJUST SETTING ais SPEAKERS ON OFF CONTROL P 0 DOLBY DIGITAL

> RX-6018 is packaging model. With SX-XSW350,SX-XSW450

#### Contents

| Safety precautions                           | 1-2  |

|----------------------------------------------|------|

| Importance administering point on the safety | 1-3  |

| Disassembly method                           | 1-4  |

| Adjustment method                            | 1-9  |

| Description of major ICs                     | 1-10 |

## Safety Precautions

- 1. This design of this product contains special hardware and many circuits and components specially for safety purposes. For continued protection, no changes should be made to the original design unless authorized in writing by the manufacturer. Replacement parts must be identical to those used in the original circuits. Services should be performed by qualified personnel only.

- 2. Alterations of the design or circuitry of the product should not be made. Any design alterations of the product should not be made. Any design alterations or additions will void the manufacturer's warranty and will further relieve the manufacture of responsibility for personal injury or property damage resulting therefrom.

- 3. Many electrical and mechanical parts in the products have special safety-related characteristics. These characteristics are often not evident from visual inspection nor can the protection afforded by them necessarily be obtained by using replacement components rated for higher voltage, wattage, etc. Replacement parts which have these special safety characteristics are identified in the Parts List of Service Manual. Electrical components having such features are identified by shading on the schematics and by ( A) on the Parts List in the Service Manual. The use of a substitute replacement which does not have the same safety characteristics as the recommended replacement parts shown in the Parts List of Service Manual may create shock, fire, or other hazards.

- 4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the like to be separated from live parts, high temperature parts, moving parts and/or sharp edges for the prevention of electric shock and fire hazard. When service is required, the original lead routing and dress should be observed, and it should be confirmed that they have been returned to normal, after re-assembling.

- 5. Leakage currnet check (Electrical shock hazard testing) After re-assembling the product, always perform an isolation check on the exposed metal parts of the product (antenna terminals, knobs, metal cabinet, screw heads, headphone jack, control shafts, etc.) to be sure the product is safe to operate without danger of electrical shock. Do not use a line isolation transformer during this check.

- Plug the AC line cord directly into the AC outlet. Using a "Leakage Current Tester", measure the leakage current from each exposed metal parts of the cabinet, particularly any exposed metal part having a return path to the chassis, to a known good earth ground. Any leakage current must not exceed 0.5mA AC (r.m.s.)

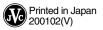

- Alternate check method

Plug the AC line cord directly into the AC outlet. Use an AC voltmeter having, 1,000 ohms per volt or more sensitivity in the following manner. Connect a  $1,500 \Omega$  10W resistor paralleled by

a 0.15 /F AC-type capacitor between an exposed metal part and a known good earth ground. Measure the AC voltage across the resistor with the AC voltmeter.

Move the resistor connection to eachexposed metal part, particularly any exposed metal part having a return path to the chassis, and meausre the AC voltage across the resistor. Now, reverse the plug in the AC outlet and repeat each measurement. voltage measured Any must not exceed 0.75 V AC (r.m.s.). This corresponds to 0.5 mA AC (r.m.s.).

#### Warning

- 1. This equipment has been designed and manufactured to meet international safety standards.

- 2. It is the legal responsibility of the repairer to ensure that these safety standards are maintained. 3. Repairs must be made in accordance with the relevant safety standards.

- 4. It is essential that safety critical components are replaced by approved parts.

- 4. It is essential that safety critical components are replaced by approved parts

- 5. If mains voltage selector is provided, check setting for local voltage.

1-2 A CAUTION Burrs formed during molding may be left over on some parts of the chassis. Therefore, pay attention to such burrs in the case of preforming repair of this system.

### Importance administering point on the safety

For USA and Canada / pour États - Unis d' Amérique et Canada

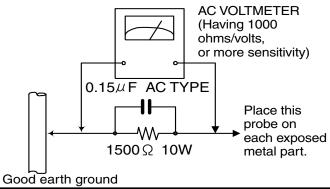

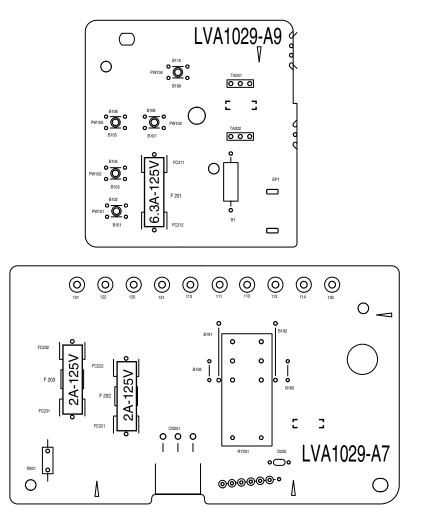

Caution: For continued protection against risk of fire, replace only with same type 6.3A/125V for F201, 2A/125V for F202 and F203. This symbol specifies type of fast operating fuse.

Précaution: Pour eviter risques de feux, remplacez le fusible de sureté de F201 comme le meme type que 6.3A/125V, et 2A/125V pour F202 et F203. Ce sont des fusibles sûretes qui functionnes rapide.

# **Disassembly method**

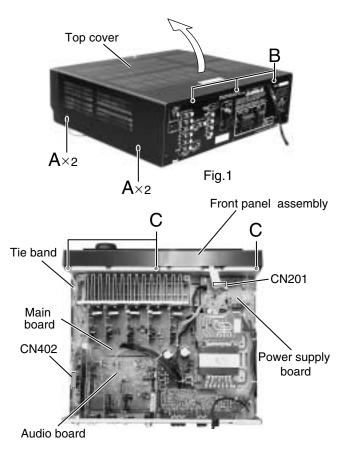

#### Removing the top cover (See Fig.1)

- 1. Remove the four screws A attaching the top cover on both sides of the body.

- 2. Remove the three screws B on the back of the body.

- 3. Remove the top cover from behind in the direction of the arrow while pulling both sides outward.

#### Removing the front panel assembly (See Fig.2 and 3)

- Prior to performing the following procedure, remove the top cover.

- 1. Disconnect the card wire from connector CN402 on the audio board and CN201 on the power supply board in the front panel assembly.

- 2. Cut off the tie band fixing the harness.

- 3. Remove the three screws C attaching the front panel assembly.

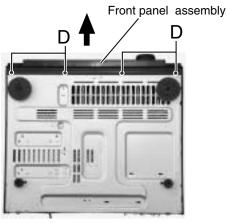

- 4. Remove the four screws D attaching the front panel assembly on the bottom of the body. Detach the front panel assembly toward the front.

Fig.2

Fig.3

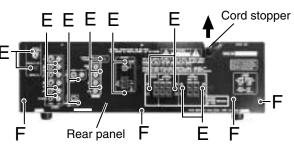

#### Removing the rear panel (See Fig.4)

- Prior to performing the following procedure, remove the top cover.

- 1. Remove the power cord stopper from the rear panel by moving it in the direction of the arrow.

- 2. Remove the seventeen screws E attaching the each boards to the rear panel on the back of the body.

- 3. Remove the four screws F attaching the rear panel on the back of the body.

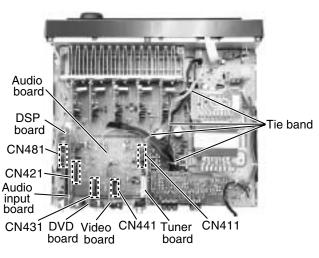

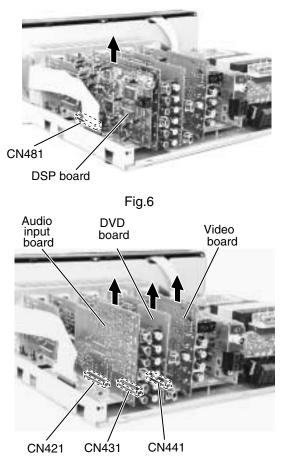

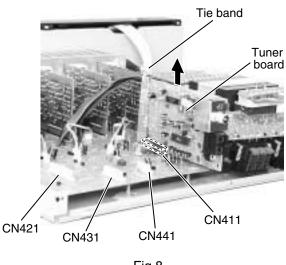

#### Removing each board connected to the rear side of the audio board (See Fig.5 to 8)

- Prior to performing the following procedure, remove the top cover and the rear panel.

- 1. Cut off the tie band fixing the harness.

- 2. Disconnect the DSP board from connector CN481 on the audio board.

- 3. Disconnect the audio input board. DVD board and the video board from connector CN421, CN431 and CN441 on the audio board.

- 4. Disconnect the tuner board from connector CN411 on the audio board.

Fig.5

Fig.7

Fig.8

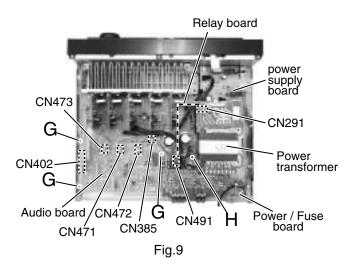

#### ■ Removing the audio board (See Fig.9)

- Prior to performing the following procedure, remove the top cover and the rear panel.

- 1. Disconnect the card wire from connector CN402 on the audio board.

- 2. Disconnect the relay board from the audio board and the power supply board. (CN291,CN491)

- 3. Disconnect the harness from connector CN473, CN471, CN472, and CN385.

- 4. Remove the three screws G attaching the audio board assembly.

- 5. Remove the screw H attaching the audio board assembly.

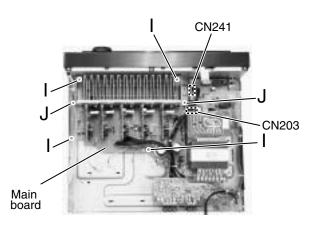

#### Removing the main board. (See Fig.10)

- Prior to performing the following procedure, remove the top cover, the rear panel and audio board.

- 1. Disconnect the harness from connector CN241 and CN203 on the power supply board respectively.

- 2. Remove the four screws I and the two screws J attaching the main board.

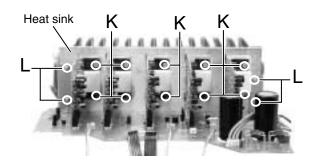

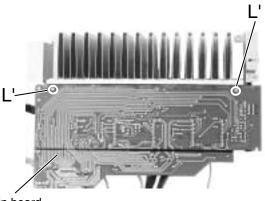

#### ■ Removing the Heat sink (See Fig.11 to 12)

- 1. Remove the ten screws K and four screws L attaching the heat sink.

- 2. Remove the two screws L' attaching the heat sink from the rear side of main board.

Fig.10

Main board rear side

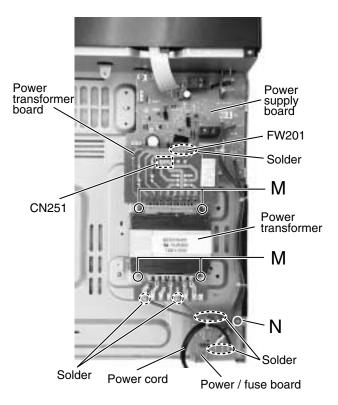

#### Removing the power transformer (See Fig.13)

- Prior to performing the following procedures, remove the top cover.

- 1. Unsolder the two harnesses connected to the power transformer.

- 2. Disconnect the harness from connector CN251 and unsolder the harnesses connected to FW201 on the power transformer board.

- 3. Remove the four screws M attaching the power transformer.

#### Removing the power / fuse board (See Fig.13)

- Prior to performing the following procedure, remove the top cover and the rear panel.

- 1. Remove the screw N attaching the power / fuse board.

- 2. Unsolder the power cord and other harnesses connected to the power / fuse board.

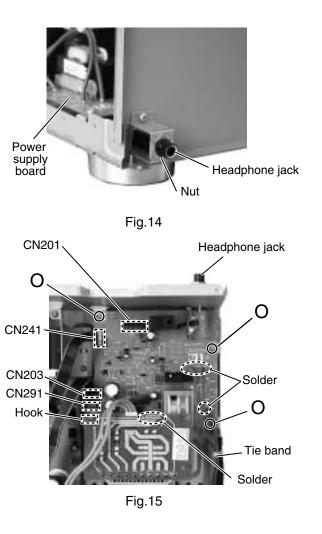

# Removing the power supply board (See Fig.14 and 15)

- Prior to performing the following procedure, remove the top cover and the front panel.

- 1. Remove the one nut attaching the headphone jack of the power supply board on the front side of the body.

- 2. Disconnect the harness connected to connector CN241,CN201,CN203 and CN291 on the power transformer board (If necessary, cut off the band fixing the harness on the side of the base chassis).

- 3. Remove the three screws O attaching the power supply board and pull out the power supply board from the front bracket backward.

- 4. Unsolder the three harnesses connected to the power supply board.

Fig.13

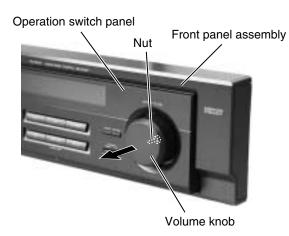

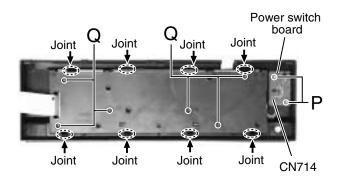

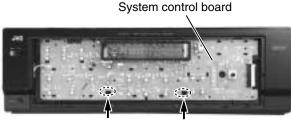

- Removing the system control board / power switch board (See Fig.16 to 18)

- Prior to performing the following procedure, remove the top cover and the front panel assembly.

- 1. Pull out the volume knob on the front side of the front panel and remove the nut attaching the system control board.

- 2. Remove the two screws P attaching the power switch board.

- 3. Disconnect the harness from connector CN714 on the power switch board.

- 4. Remove the six screws Q attaching the system control board on the back of the front panel.

- On the back of the front panel, release the eight joints by pushing the joint tabs inward. Remove the operation switch panel toward the front.

- 6. Release the two hook attaching the system control board.

Fig.16

Fig.17

Hook Hook

Fig.18

# Adjustment method

#### Tuner section

1.Tuner range

FM

87.5MHz~108.0MHz

AM(MW)

530kHz~1710kHz

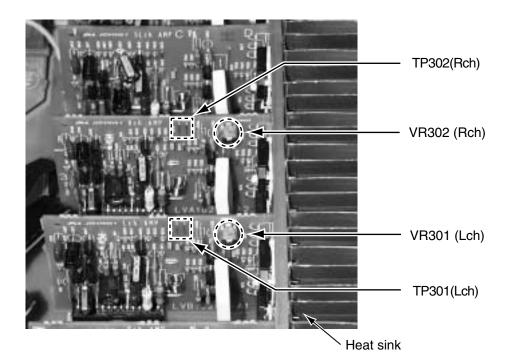

#### Power amplifier section

#### Adjustment of idling current

| Measurement location | TP301(Lch) , TP302(Rch) |

|----------------------|-------------------------|

| Adjustment part      | VR301(Lch) , VR302(Rch) |

#### Attention

This adjustment does not obtain a correct adjustment value immediately after the amplifier is used (state that an internal temperature has risen).

Please adjust immediately after using the amplifier after turning off the power supply of the amplifier and falling an internal temperature.

<Adjustment method>

- 1.Set the volume control to minimum during this adjustment.(No signal & No load)

- 2.Set the surround mode OFF.

- 2.Turn VR301 and VR302 fully counterclockwise to warm up before adjustment.

If the heat sink is already warm from previous use the correct adjustment can not be made.

- 3.For L-ch,connect a DC voltmeter between TP301's B216 and B217 (Lch) And,connect it between TP302's B218 and B219(Rch).

- 4.30 minutes later after power on, adjust VR301 for L-ch, or VR302 for R-ch so that the DC voltmeter value has 1mV~10mV.

- \* It is not abnormal though the idling current might not become 0mA even if it is finished to turn variable resistance (VR301,VR302) in the direction of counterclockwise.

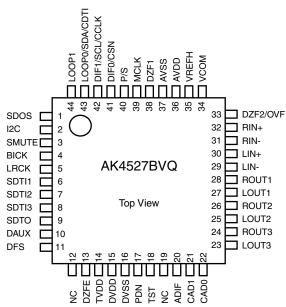

### **Description of major ICs** ■ AK4527B (IC601) : A/D,D/A Converter

1.Pin layout

#### 2. Pin function (1/2)

| 2. Pin f | function (1/2 | )   | AK4527(1/2)                                                                          |  |  |  |

|----------|---------------|-----|--------------------------------------------------------------------------------------|--|--|--|

| No.      | Pin name      | I/O | Function                                                                             |  |  |  |

| 1        | SDOS          | Ι   | SDTO Source Select Pin (Note 1)                                                      |  |  |  |

|          |               |     | "L" : Internal ADC output, "H" : DAUX input                                          |  |  |  |

| 2        | I2C           | I   | Control Mode Select Pin                                                              |  |  |  |

|          |               |     | "L" : 3-wire Serial, "H" : I2C Bus                                                   |  |  |  |

| 3        | SMUTE         | I   | Soft Mute Pin (Note 1)                                                               |  |  |  |

|          |               |     | When this pin goes to "H", soft mute cycle is initialized.                           |  |  |  |

|          |               |     | When returning to "L", the output mute releases.                                     |  |  |  |

| 4        | BICK          | I   | Audio Serial Data Clock Pin                                                          |  |  |  |

| 5        | LRCK          | I/O | Input Channel Clock Pin                                                              |  |  |  |

| 6        | SDTI1         | I   | DAC1 Audio Serial Data Input Pin                                                     |  |  |  |

| 7        | SDTI2         | I   | DAC2 Audio Serial Data Input Pin                                                     |  |  |  |

| 8        | SDTI3         | I   | DAC3 Audio Serial Data Input Pin                                                     |  |  |  |

| 9        | SDTO          | 0   | Audio Serial Data Output Pin                                                         |  |  |  |

| 10       | DAUX          | Ι   | Sub Audio Serial Data Input Pin                                                      |  |  |  |

| 11       | DFS           | I   | Double Speed Sampling Mode Pin (Note 1)                                              |  |  |  |

|          |               |     | "L" : Normal Speed, "H" : Double Speed                                               |  |  |  |

| 12       | NC            | -   | No Connect                                                                           |  |  |  |

|          |               |     | No internal bonding.                                                                 |  |  |  |

| 13       | DZEF          | I   | Zero Input Detect Enable Pin                                                         |  |  |  |

|          |               |     | "L" : mode 7 (disable) at parallel mode,                                             |  |  |  |

|          |               |     | zero detect mode is selectable by DZFM2-0 bits at serial mode.                       |  |  |  |

|          |               |     | "H" : mode 0 (DZF is AND of all six channels)                                        |  |  |  |

| 14       | TVDD          | -   | Output Buffer Power supply Pin, 2.7V~5.5V                                            |  |  |  |

| 15       | DVDD          | -   | Digital Power Supply Pin, 4.5V~5.5V                                                  |  |  |  |

| 16       | DVSS          | -   | De-emphasis Pin, 0V                                                                  |  |  |  |

| 17       | PDN           | Ι   | Power-Down & Reset Pin                                                               |  |  |  |

|          |               |     | When "L", the AK4527B is powered-down and the control registers are reset to default |  |  |  |

|          |               |     | state. If the state of P/S or CAD0-1 changes, then the AK4527B must be reset by PDN. |  |  |  |

| 18       | TST           | Ι   | Test Pin                                                                             |  |  |  |

|          |               |     | This pin should be connected to DVSS.                                                |  |  |  |

1-10

|     | nction (2/2) |     | AK4527(1/2)                                                                           |

|-----|--------------|-----|---------------------------------------------------------------------------------------|

| No. | Pin name     | I/O | No Connect Function                                                                   |

| 19  | NC           | -   | No internal bonding.                                                                  |

|     |              |     | Analog Input Format Select Pin                                                        |

| 20  | ADIF         | I   | "H" : Full-differential input, "L" : Single-ended input                               |

|     |              |     | Chip Address 1 Pin                                                                    |

| 21  | CAD1         | I   | Chip Address 0 Pin                                                                    |

| 22  | CAD0         |     | DAC3 Lch Analog Output Pin                                                            |

| 23  | LOUT3        | 0   | DAC3 Rch Analog Output Pin                                                            |

| 24  | ROUT3        | 0   | DAC2 Lch Analog Output Pin                                                            |

| 25  | LOUT2        | 0   | DAC2 Rch Analog Output Pin                                                            |

| 26  | ROUT2        | 0   | DAC1 Lch Analog Output Pin                                                            |

| 27  | LOUT1        | 0   | DAC1 Rch Analog Output Pin                                                            |

| 28  | ROUT1        | 0   | Lch Analog Negative Input Pin                                                         |

| 29  | LIN-         | I   | Lch Analog Positive Input Pin                                                         |

| 30  | LIN+         | Ι   | Rch Analog Negative Input Pin                                                         |

| 31  | RIN-         | I   | Rch Analog Positive Input Pin                                                         |

| 32  | RIN+         | I   | Zero Input Detect 2 Pin (Note 2)                                                      |

| 33  | DZF2         | 0   | When the input data of the group 1 follow total 8192LRCK cycles with "0" input data,  |

|     |              |     | this pin goes to "H".                                                                 |

|     |              |     | Analog Input Overflow Detect Pin (Note 3)                                             |

|     | OVF          | 0   | This pin goes to "H" if the analog input of Lch or Rch is overflows.                  |

|     |              |     | Common Voltage Output Pin,AVDD/2                                                      |

| 34  | VCOM         | 0   | Large external capacitor around 2.2uF is used to reduce power-supply noise.           |

|     |              |     | Positive Voltage Reference Input Pin,AVDD                                             |

| 35  | VREFH        | 1   | Analog Power Supply Pin,4.5V~5.5V                                                     |

| 36  | AVDD         | -   | Analog Ground Pin,0V                                                                  |

| 37  | AVSS         | -   | Zero Input Detect 1 Pin (Note 2)                                                      |

| 38  | DZF1         | 0   | When the input data of the group 1 follow total 8192 LRCK cycles with "0" input data, |

|     |              |     | this pin goes to "H".                                                                 |

|     |              |     | Master Clock Input Pin                                                                |

| 39  | MCLK         | 1   | Parallel / Serial Select Pin                                                          |

| 40  | P/S          | 1   | "L" : Serial control mode, "H" : Parallel control mode                                |

|     |              | •   | Audio Data Interface Format 0 Pin in parallel mode                                    |

| 41  | DIF0         | 1   | Chip select pin in 3-wire serial control mode                                         |

|     | CSN          |     | This pin should be connected to DVDD at I2C bus control mode                          |

|     | 0011         | •   | Audio Data Interface Format 1 Pin in parallel mode                                    |

| 42  | DIF1         | 1   | Control Data Clock Pin in serial control mode                                         |

|     | SCL/CCLK     |     | I2C = "L" : CCLK(3-wire Serial), I2C = "H" : SCL(I2CBus)                              |

|     |              |     | Loopback Mode 0 Pin in parallel control mode                                          |

| 43  | LOOP0        | 1   | Enables digital loop-back from ADC to 3 DACs.                                         |

| -0  |              | I.  | Control Data Input Pin in serial control mode                                         |

|     | SAD/CDTI     | I/O | I2C = "L" : CDTI(3-wire Serial), I2C = "H" : SDA(I2CBus)                              |

|     |              | 1/0 | Loopback Mode 1 Pin (Note 1)                                                          |

| 44  | LOOP1        | 1   | Enable all 3 DAC channels to be input from SDTII.                                     |

| 44  |              |     | $\Box$                 |

Notes : 1. SDOS, SMUTE, DFS, and LOOP1 pins are ORed with register data if P/S = "L".

- 2. The group 1 and 2 can be selected by DZFM2-0 bit if P/S = "L" and DZFME = "L".

- 3. This pin becomes OVF pin if OVFE bit is set to "1" at serial control mode.

- 4. All input pins should not be left floating.

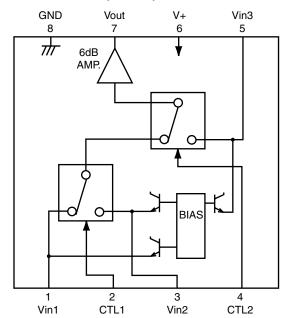

#### ■ TC9164AN (IC402): Analog switch

- 1.Function

- Switch to On/Off of S1 to S8 by control of LSI.

- 2.Terminal Lay out & Block Diagram

#### ■ NJM2246D(IC501):Video switch

|       |       | -      |

|-------|-------|--------|

| CTL 1 | CTL 2 | Output |

| L     | L     | VIN 1  |

| Н     | L     | VIN 2  |

| L/H   | н     | VIN 3  |

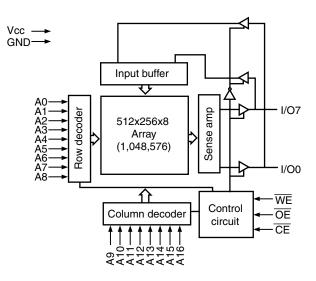

#### AS7C31025-15 (IC641) : CMOS SRAM

Block diagram

#### Pin layout

|                                                                                                                                    | 32-pin TSOP II                                                                      |                       |                                                                                  |                                                                                                         |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|

| A0 E<br>A1 L<br>A2 L<br>A3 E<br>I/O0 L<br>I/O1 L<br>Vcc L<br>GNDE<br>I/O2 L<br>I/O2 L<br>I/O3 L<br>WE A4 L<br>A5 L<br>A6 L<br>A7 L | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16 | AS7C1025<br>AS7C31025 | 32<br>31<br>30<br>29<br>27<br>26<br>25<br>24<br>22<br>21<br>20<br>19<br>18<br>17 | A16<br>A15<br>A14<br>A13<br>VO7<br>VC7<br>VC6<br>VC05<br>VC05<br>VC05<br>VC05<br>A11<br>A10<br>A9<br>A8 |  |  |  |

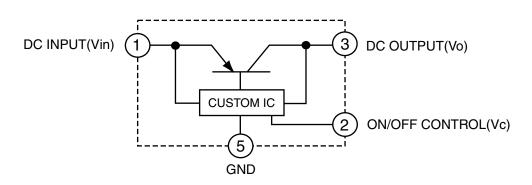

#### PQ3DZ53 (IC681) : Regulator IC

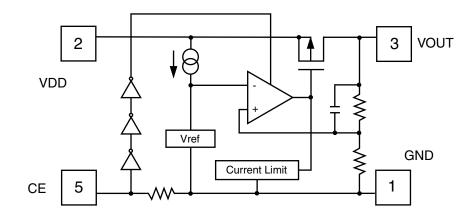

#### RN5RZ33BA (IC683) : Voltage Regurator

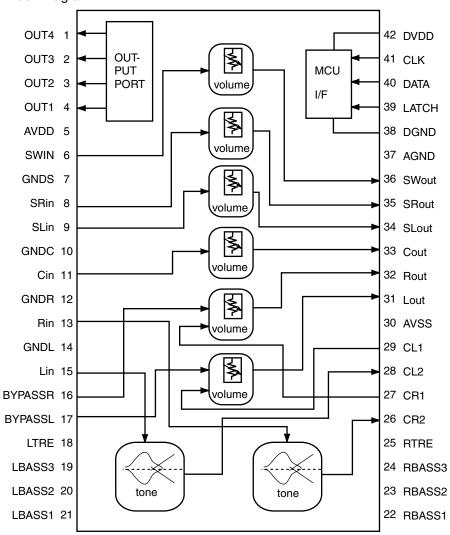

#### M62446FP(IC428) : 6CH Master volume

1.Block Diagram

2.Pin Function

| Pin No. | Symbol     | I/O | Descriptions                                        |

|---------|------------|-----|-----------------------------------------------------|

| 1       | SURROUND   | 0   | SURROUND control terminal                           |

| 2       | BASS BOOST | 0   | BASS BOOST control terminal                         |

| 3       | INPUT-ATT  | 0   | Input attenuator control terminal                   |

| 4       | MUTING     | 0   | MUTING control terminal                             |

| 5       | AVDD       | -   | Analog positive power supply terminal               |

| 6       | SWIN       | I   | SUB Woofer volume signal input terminal             |

| 7       | A.GND      | -   | Analog ground terminal                              |

| 8       | RR IN      | I   | R ch volume signal input terminal for rear speaker  |

| 9       | RL IN      | I   | L ch volume signal input terminal for rear speaker  |

| 10      | A.GND      | -   | Analog ground terminal                              |

| 11      | C IN       | I   | Center volume signal input terminal                 |

| 12      | A.GND      | -   | Analog ground terminal                              |

| 13      | R IN       | I   | R ch volume signal input terminal                   |

| 14      | A.GND      | -   | Analog ground terminal                              |

| 15      | L IN       | I   | L ch volume signal input terminal                   |

| 16,17   | BYPASSR,L  | -   | Non connect                                         |

| 18      | LTRE       | -   | Frequency adjustment terminal tone/treble           |

| 19~21   | LBASS3~1   | -   | Frequency adjustment terminal tone/bass             |

| 22      | CR2        | 0   | Tone output terminal                                |

| 23,24   | RBASS2,4   | -   | Frequency adjustment terminal tone/bass             |

| 25      | RTRE       | -   | Frequency adjustment terminal tone/treble           |

| 26      | RBASS1     | -   | Frequency adjustment terminal tone/bass             |

| 27      | CR1        |     | L/R volume input terminal                           |

| 28      | CL2        | 0   | Tone output terminal                                |

| 29      | CL1        | I   | L/R volume input terminal                           |

| 30      | AVSS       | -   | Analog negative power supply terminal               |

| 31      | L OUT      | 0   | L ch output                                         |

| 32      | R OUT      | 0   | R ch output                                         |

| 33      | C OUT      | 0   | Center volume signal output terminal                |

| 34      | RL OUT     | 0   | L ch volume signal output terminal for rear speaker |

| 35      | RR OUT     | 0   | R ch volume signal output terminal for rear speaker |

| 36      | SW OUT     | 0   | SUB Woofer volume signal output terminal            |

| 37      | A.GND      | -   | Analog ground terminal                              |

| 38      | D.GND      | -   | Digital ground terminal                             |

| 39      | VOL STB    | I   | Latch input terminal                                |

| 40      | VOL DATA   |     | Volume data input terminal                          |

| 41      | VOL CLK    |     | Clock input terminal for data transfer              |

| 42      | DVDD       | -   | Digital power supply terminal                       |

#### MN101C35DHK1 (IC701) : System controller

| _  |     |   |    | - |

|----|-----|---|----|---|

| Γ  | 100 | ~ | 76 |   |

| 1  |     |   | 75 |   |

| ٢  |     |   | ٢  |   |

| 25 |     |   | 51 |   |

|    | 26  | ~ | 50 |   |

#### Pin function (1/2)

| Pin No. | Symbol          | I/O | Function           |

|---------|-----------------|-----|--------------------|

| 1       | TXD/SB00/P00    | I   | VOL.JOG IN_1       |

| 2       | RXD/SBI0/P01    | I   | VOL.JOG IN_2       |

| 3       | SBT0/P02        | I/O | DATA (PLL)         |

| 4       | SB01/P03        | 0   | CLK (PLL)          |

| 5       | SBI1/P04        | 0   | DE (PLL)           |

| 6       | SBT1/P05        | l   | VIDEO S/C DVD      |

| 7       | BUZZER/P06      | I   | VIDEO S/C VCR      |

| 8       | VDD             | -   | Power supply +5V   |

| 9,10    | OSC1,2          | I/O | OSC (8MHz)         |

| 11      | VSS             | -   | GND                |

| 12      | XI              | I   | GND                |

| 13      | X0              | 0   | OPEN               |

| 14      | MMOD            | I   | GND                |

| 15      | VREF-           | -   | GND                |

| 16      | AN0/PA0         | I   | KEY INPUT 1 (7KEY) |

| 17      | AN1/PA1         |     | KEY INPUT 2 (7KEY) |

| 18      | AN2/PA2         | I   | KEY INPUT 3 (7KEY) |

| 19      | AN3/PA3         | I   | KEY INPUT 4 (7KEY) |

| 20      | AN4/PA4         | I   | KEY INPUT 5 (7KEY) |

| 21      | AN5/PA5         | I   | INH IN             |

| 22      | AN5/PA5         | I   | CHIP SELECT 1      |

| 23      | AN5/PA5         | I   | CHIP SELECT 2      |

| 24      | VREF+           | -   | Power supply +5V   |

| 25      | P07             | I   | VIDEO S/C DBS      |

| 26      | RST /P27        |     | RESET INPUT        |

| 27      | RNOUT/TM0I0/P10 | 0   | RDS CLK OUT (RDS)  |

| 28      | TM1I0/P11       | I   | DCS INPUT          |

| 29      | TM2I0/P12       | 0   | DCS OUTPUT         |

| 30      | TM3I0/P13       | I   | AVLINK VCR IN      |

| 31      | TM4I0/P14       | 0   | AVLINK VCR OUT     |

| 32      | P15             | I/O | RDS DATA (RDS)     |

| 33      | IRQ0/P20        | I   | PROTECTOR IN       |

| 34      | SENS/IRQ1/P21   | I   | REMOCON INPUT      |

| 35      | IRQ2/P22        |     | TUNED IN (TUNER)   |

| 36      | IRQ3/P23        |     | STEREO IN (TUNER)  |

| 37      | IRQ4/P24        | I   | RDS DAVN (RDS)     |

| 38      | P25             |     | SELF CHECK INPUT   |

| 39      | SB02/P30        | 0   | COMMAND (DSP)      |

| 40      | SBI2/P31        | I   | STATUS (DSP)       |

#### Pin function (2/2)

| Pin No. | Symbol    | I/O | Function                            |

|---------|-----------|-----|-------------------------------------|

| 41      | SBT2/P32  | 0   | CLK (DSP)                           |

| 42      | P50       | 0   | READY (DSP)                         |

| 43      | P51       | 0   | RESET (DSP)                         |

| 44      | P52       | 0   | RELAY S                             |

| 45      | P53       | 0   | RELAY C                             |

| 46      | P54       | 0   | RELAY L/R 1                         |

| 47      | DGT17/P67 | 0   | RELAY L/R 2                         |

| 48      | DGT16/P66 | 0   | RELAY HEADPHONE                     |

| 49~64   | G16~G1    | 0   | FL GRID SIGNAL CONTROL OUT          |

| 65~80   | P87~P90   | 0   | FL SEGMENT SIGNAL CONTROL OUT       |

| 81      | SEG24/PC2 | 0   | LED8 SIGNAL CONTROL OUT (FM/AM)     |

| 82      | SEG25/PC1 | 0   | LED7 SIGNAL CONTROL OUT (TV/DBS)    |

| 83      | SEG26/PC0 | 0   | LED6 SIGNAL CONTROL OUT (TAPE/CDR)  |

| 84      | SEG27/PB7 | 0   | LED5 SIGNAL CONTROL OUT (VCR)       |

| 85      | SEG28/PB6 | 0   | LED4 SIGNAL CONTROL OUT (CD)        |

| 86      | SEG29/PB5 | 0   | LED3 SIGNAL CONTROL OUT (DVD)       |

| 87      | SEG30/PB4 | 0   | LED2 SIGNAL CONTROL OUT (PHONO)     |

| 88      | SEG31/PB3 | 0   | LED1 SIGNAL CONTROL OUT (DVD MULTI) |

| 89      | SEG32/PB2 | 0   | SOUSE MUTE                          |

| 90      | SEG33/PB1 | 0   | SUBWOOFER MUTE                      |

| 91      | SEG34/PB0 | 0   | TUNER MUTE                          |

| 92      | SEG35/PD7 | 0   | POWER ON (STANDBY)                  |

| 93      | SEG36/PD6 | 0   | SURROUND                            |

| 94      | SEG37/PD5 | 0   | DATA (A.SW)                         |

| 95      | SEG38/PD4 | 0   | CLK (A.SW)                          |

| 96      | SEG39/PD3 | 0   | STB (A.SW)                          |

| 97      | SEG40/PD2 | 0   | LATCH (A.SW)                        |

| 98      | SEG41/PD1 | 0   | DATA (VOL)                          |

| 99      | SEG42/PD0 | 0   | CLK (VOL)                           |

| 100     | VPP       | 0   | VPP                                 |

#### ■ TC9446F-014(IC631):Digital signal processor for dolby digital (AC-3) / MPEG2 audio decode

| Pin No. | Symbol          | I/O  | Function                                                                  |

|---------|-----------------|------|---------------------------------------------------------------------------|

| 1       | RST             | I    | Reset signal input terminal (L:reset H:Operation usually)                 |

| 2       | MIMD            | I    | Microcomputer interface mode selection input terminal (L:serial H:IC bus) |

| 3       | MICS            | I    | Microcomputer interface chip select input terminal                        |

| 4       | MILP            | I    | Microcomputer interface latch pulse input                                 |

| 5       | MIDIO           | I/O  | Microcomputer interface data I/O terminal                                 |

| 6       | MICK            |      | Microcomputer interface clock input terminal                              |

| 7       | MIACK           | 0    | Microcomputer interface acknowledge output terminal                       |

| 8~11    | FI0~3           | I    | Flag input terminal 0~3                                                   |

| 12      | IRQ             | I    | Interrupt input terminal                                                  |

| 13      | VSS             | -    | Digital ground terminal                                                   |

| 14      | LRCKA           | 1    | Audio interface LR clock input terminal A                                 |

| 15      | BCKA            | 1    | Audio interface bit clock input terminal A                                |

| 16~18   | SDO0~2          | Ó    | Audio interface data output terminal 0                                    |

| 19      | SD03            | -    | Non connect                                                               |

| 20      | LRCKB           |      | Audio interface LR clock input terminal B                                 |

| 21      | BCKB            | i    | Audio interface bit clock input terminal B                                |

| 22      | SDT0            |      | Audio interface data input terminal 0                                     |

| 23      | SDT0            |      | Audio interface data input terminal 1                                     |

| 20      | VDD             | -    | Power supply for digital circuit                                          |

| 24      | LRCKOA          | 0    | Audio interface LR clock output terminal A                                |

| 25      | BCKOA           | 0    | Audio interface bit clock output terminal A                               |

| 27,28   | TEST0,1         |      | Test input terminal 0/1 (L:test H:operation usually)                      |

| 29~31   |                 | -    | Non connect                                                               |

|         |                 | -    |                                                                           |

| 32,33   | TEST2,3         |      | Test input terminal (L:test H:operation usually)                          |

| 34      | RX              | l    | SPDIF input terminal                                                      |

| 35      | VSS             | -    | Ground terminal for digital circuit                                       |

| 36      | TSTSUBO         |      | Test sub input terminal 0 (L:test H:operation usually)                    |

| 37      | FCONT           | 0    | VCO Frequency control output terminal                                     |

| 38,39   | TSTSUB1,TSTSUB2 |      | Test sub input terminal 1,2 (L:test H:operation usually)                  |

| 40      | PDO             | 0    | Phase error signal output terminal                                        |

| 41      | VDDA            | -    | Power supply for analog circuit                                           |

| 42      | PLON            | <br> | Clock selection input terminal (L:external clock H:VCO clock)             |

| 43      | AMPI            |      | AMP.input terminal for LPF                                                |

| 44      | AMPO            | 0    | AMP.output terminal for LPF                                               |

| 45      | CKI             | I    | External clock input terminal                                             |

| 46      | VSSA            | -    | Ground terminal for analog circuit                                        |

| 47      | СКО             | 0    | DIR Clock output terminal                                                 |

| 48      | LOCK            | 0    | VCO Lock detection output terminal                                        |

| 49      | VSS             | -    | Ground terminal for digital circuit                                       |

| 50      | WR              | 0    | External SRAM writing signal output terminal                              |

| 51      | OE              | 0    | External SRAM output enable signal output terminal                        |

| 52      | CE              | 0    | External SRAM chip enable signal output terminal                          |

| 53      | VDD             | -    | Power supply terminal for digital circuit                                 |

| 54~61   | IO7~0           | I/O  | External SRAM data I/O terminal 7~0                                       |

| 62      | VSS             | -    | Ground terminal for digital circuit                                       |

| 63~70   | AD0~7           | 0    | External SRAM address output terminal 0~7                                 |

| 71      | VDD             | -    | Power supply terminal for digital circuit                                 |

| 72~80   | AD8~16          | 0    | External SRAM address output terminal 8~16                                |

| 81      | VSS             | -    | Ground terminal for digital circuit                                       |

| 82~89   | PO0~7           | 0    | General purpose output terminal 0~7                                       |

| 90      | VDDDL           | -    | Power supply terminal for DLL                                             |

| 91      | LPFO            | 0    | LPF output terminal for DLL                                               |

| 92,93   | DLON, DLCKS     | I    | Refer to the undermentioned table                                         |

| 94      | SCKO            | -    | Non connect                                                               |

| 95      | VSSDL           | -    | Ground terminal for DLL                                                   |

| 96      | SCKI            | I    | External system clock input terminal                                      |

| 97      | VSSX            | -    | Ground termonal for oscillation circuit                                   |

|         |                 | I/O  | Oscillation I/O terminal                                                  |

| 98,99   | XO,XI           | 1/0  | Oscillation I/O terminal                                                  |

| DLCKS terminal | DLONterminal         | DLL clock setting            |  |

|----------------|----------------------|------------------------------|--|

| L              | L                    | SCKI input (DLL circuit OFF) |  |

| L              | Н                    | Four times XI clock          |  |

| Н              | L                    | Three times XI clock         |  |

| H              | H Six times XI clock |                              |  |

# ■ UPD784215AGC103(IC671):UNIT CPU 1.Pin layout

|     | 75 | ~ | 51 |    |  |

|-----|----|---|----|----|--|

| 76  |    |   |    | 50 |  |

| ł   |    |   |    | ١  |  |

| 100 | 1  | ~ | 25 | 26 |  |

#### 2.Pin function

| Pin No.  | Symbol       | I/O | Function                                                  |

|----------|--------------|-----|-----------------------------------------------------------|

| 1~8      |              | -   | Non connect                                               |

| 9        | VDD          |     | Power supply terminal                                     |

| 10       | X2           | 0   | Connecting the crystal oscillator for system main clock   |

| 11       | X1           | Ť   | Connecting the crystal oscillator for system main clock   |

| 12       | VSS          | -   | Connect to GND                                            |

| 13       | XT2          | 0   | Connecting the crystal oscillator for system sub clock    |

| 14       | XT2<br>XT1   |     | Connecting the crystal oscillator for system sub clock    |

| 15       | RESET        |     | System reset signal input                                 |

| 16       | AUTODATA     |     | Output of DSP to general-purpose port                     |

| 17       | LOCK         |     | Output of DSP to general-purpose port                     |

| 18       | DIGITALO     |     | Output of DSP to general-purpose port                     |

| 19       | FORMAT       |     | Output of DSP to general-purpose port                     |

|          |              |     |                                                           |

| 20       | CHANNEL      |     | Output of DSP to general-purpose port                     |

| 21<br>22 | ERR          |     | Output of DSP to general-purpose port                     |

|          | RSTDET       |     | Reset signal input                                        |

| 23       | AVDD         | -   | Power supply terminal                                     |

| 24       | AVREF0       | -   | Connect to GND                                            |

| 25~32    |              | -   | Connect to GND                                            |

| 33       | AVSS         | -   | Connect to GND                                            |

| 34,35    |              | -   | Non connect                                               |

| 36       | AV REF1      | -   | Power supply terminal                                     |

| 37,38    | RX,TX        | -   | Not use                                                   |

| 39       |              | -   | Non connect                                               |

| 40       | DSPCOM       |     | Communication port from IC701                             |

| 41       | DSPSTS       | 0   | Status communication port to IC701                        |

| 42       | DSPCLK       |     | Clock input from IC701                                    |

| 43       | DSPRDY       |     | Ready signal input from IC701                             |

| 44       |              | -   | Non connect                                               |

| 45,46    | MIDIO_IN/OUT | I/O | Interface I/O terminal with microcomputer                 |

| 47       | MICK         | 0   | Interface I/O terminal with microcomputer of clock signal |

| 48       | MICS         | 0   | Interface I/O terminal with microcomputer of chip select  |

| 49       | MILP         | 0   | Interface I/O termonal with microcomputer                 |

| 50       | MIACK        | 0   | Interface I/O termonal with microcomputer                 |

| 51,52    |              | -   | Non connect                                               |

| 53       | DSPRST       | 0   | Reset signal output of DSP                                |

| 54~63    |              | -   | Non connect                                               |

| 64,65    | CDTI/CDTO    | I/O | Interface I/O terminal with microcomputer                 |

| 66       | CCLK         | 0   | Interface I/O terminal with microcomputer of clock signal |

| 67       | CS           | 0   | Interface I/O terminal with microcomputer of chip select  |

| 68       | XTS          | 0   | OSC Select                                                |

| 69,70    |              | -   | Non connect                                               |

| 71       | PD           | 0   | Reset signal output                                       |

| 72       | GND          | -   | Connect to GND                                            |

| 73~80    |              | -   | Non connect                                               |

| 81       | VDD          | -   | Power supply                                              |

| 82       | 3D-ON        | -   | Non connect                                               |

| 83       | 3D-ON        | 0   | Switch at output destination of surround channel          |

| 84       | ANA/T-TONE   | 0   | Test tone control                                         |

| 85       | REF-MIX      | 0   | Control at output destination of LFE channel              |

| 86       |              | -   | Non connect                                               |

| 87       | D.MUTE       | 0   | Mute of the digital out terminal is controlled            |

| 88       | S.MUTE       | 0   | Mute of the audio signal is controlled                    |

| 89       |              | -   | Non connect                                               |

| 90~93    | ASW1~4       | 0   | Selection of digital input selector                       |

| 94       | TEST         | -   | Test terminal                                             |

| 95~100   |              | -   | Non connect                                               |

|          |              | 1   |                                                           |